# 基于 ARM 和 FPGA 设计的电机控制 SiP 电路

武明月，杜存玉，陈涛，艾亚辉

(中国电子科技集团公司 第五十八研究所，江苏 无锡 214026)

**摘要：**传统电机控制电路一般采用分立元件，按照特定的互联关系和约束规则布局在 PCB 板上，其尺寸较大且可靠性不高，越来越无法满足电机控制系统小型化、轻量化的需求。系统级封装（System in Package）是利用先进的工艺在一个封装基板上组件和集成多个 IC 芯片以及不同类型的元器件，构成复杂且具有特定功能的电子信息系统。基于系统级封装技术设计了一款电机控制 SiP 电路，该 SiP 集成了一颗 ARM 裸芯和一颗 FPGA 裸芯，二者通过 Wire-bond 工艺连接于 PBGA321 基板形成 SiP 电路。电机控制 SiP 体积比 ARM 和 FPGA 分立器件设计的电机控制系统缩小了 50% 以上，重量减轻 60% 以上。解决上述传统 PCB 板级电机控制电路存在的尺寸大问题，达到小型化和高可靠性的目的。测试结果表明，该电路满足设计要求，在电机控制领域具有一定应用前景。

**关键词：**Wire-bond；系统级封装；ARM；FPGA；电机控制；PBGA；小型化

中图分类号：TN454-34 文献标识码：A

Design of motor control SiP circuit based on ARM and FPGA

WU Mingyue, DU Cunyu, CHEN Tao, AI Yahui

(No.58 Research Institute, China Electronics Technology Group Corporation, Wuxi 214026, China)

**Abstract:** Traditional motor control circuits generally use discrete components and are laid out on PCB boards according to specific interconnection relationships and constraint rules. They are large in size and have low reliability, and are increasingly unable to meet the needs of miniaturization and lightweight motor control systems. SiP (system in package) is the utilization of advanced technology to assemble and integrate multiple IC chips and different types of components on a single package substrate, forming a complex electronic information system with specific functions. An S motor control SiP circuit is designed based on SiP technology. The SiP integrates an ARM (advanced RISC machine) bare core and an FPGA (field programmable gate array) bare core, which are connected to the PBGA (plastic ball grid arra) 321 substrate by means of wire-bonding process to form a SiP circuit. The volume of the motor control SiP is more than 50% smaller than that of the motor control system designed with ARM and FPGA discrete devices, and the weight is reduced by more than 60%. The problem of large size of the traditional PCB board-level motor control circuit is solved, so as to achieve the purpose of miniaturization and high reliability. The testing results show that the circuit can meet the design requirements and has a certain application scenarios in the field of motor control.

**Keywords:** Wird-bond; system in package; ARM; FPGA; motor control; PBGA; miniaturization

## 0 引言

电机的应用越来越广泛，对电机控制的精度、可靠性和灵活性要求也越来越高。基于 ARM+FPGA 系统的电机控制电路可实现对驱动电机的高效矢量控制，高精度定位，广泛应用于工业自动化、新能源汽车及智能家居领域。而在一些对空间要求极为严苛的应用场景中，ARM 和 FPGA 芯片及其外围电路所占用的空间较大，难以满足小型化的设计需求。

随着集成电路封装技术发展，SiP 采用多芯片

单封装可以大幅度降低电路占用面积，减低功耗，提高系统可靠性，并减低成本<sup>[1-4]</sup>。基于此，本文设计了一款基于 Wire-bond 工艺，将 ARM 和 FPGA 裸芯平铺在塑封基板上，通过走线互联，再将需要的信号和电源进行引出的电机控制 SiP 电路，该 SiP 电路大幅度减小模块尺寸，能够有效解决上述问题。

## 1 电机控制 SiP 电路的设计

电机控制 SiP 集成了一颗 ARM 裸芯和一颗高云

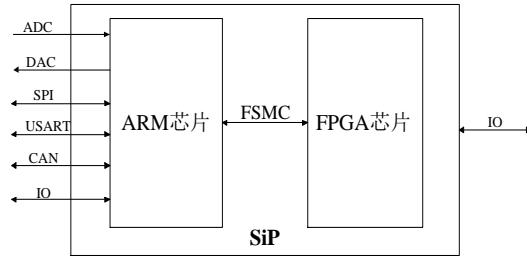

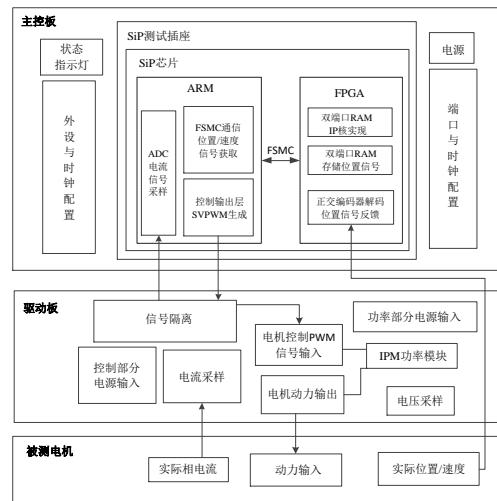

FPGA 裸芯，两颗裸芯在电路内部通过 FSMC 总线<sup>[5]</sup>实现互联。其中 ARM 作为主控芯片，处理 FPGA 采集到的电机位置、速度等数据，并输出 PWM 波驱动 IPM 模块和电机，从而实现电机控制。SiP 电路框图如图 1 所示。

图 1 电机控制 SiP 电路框图

SiP独特的ARM + FPGA的双核结构，使得其能用于诸多测试测量及控制领域。ARM采用Cortex-M4F内核的CKS32F407IGT6，其不但具有168 MHz主频、FPU浮点单元、DSP指令集等高性能特性，而且具有多外设、多接口及多I/O特性。ARM作为CPU角色负责功能实现、事件处理及接口等功能。FPGA采用高云GW1N-4K型产品，具有功耗低、性能强、资源多、使用方便等优点。FPGA作为逻辑器件，负责并行处理、实时性处理及逻辑管理等功能。ARM和FPGA采用FSMC并行总线通信，并行总线的高带宽性和易用性保证了两个芯片数据交换的便利性及实时性，以应对越来越高的测试测量及自动控制类产品功能、性能的需求。

## 2 基板设计

基板原理图设计软件选用Cadence平台Orcad组件<sup>[6]</sup>。ARM裸芯共引出144个引脚；FPGA裸芯1.2 V核电源、3.3 V电源、4组BANK电源、地、I/O 信号的PAD均引出；3.3 V电源、1.2 V核电源、地在基板上分别进行互联；每组BANK电源至少引出1组。

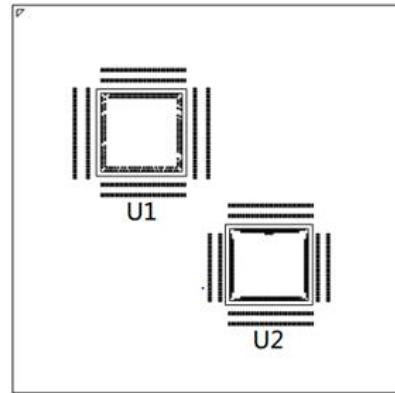

基板版图设计选用的软件为Cadence平台SiP组件。采用SiP技术将1颗ARM芯片和1颗FPGA芯片封装在1个PBGA321基板上，ARM与FPGA互连的32根FSMC信号线走线需等长，装配位置图如图2所示，

图中U1为ARM芯片，U2为FPGA芯片。

图 2 SiP 电路装配位置图

基板设计为4层，信号互联主要在TOP层完成，第二层为电源与地层，第三层为主要FSMC信号互连层，Bottom层为SiP对外引出信号连接到BGA球的布线。电机控制SiP电路结构框图如图3所示。

图 3 电机控制 SiP 电路结构框图

在设计中还应该注意到，由于BT基板厚度很薄，很容易出现翘曲的问题。可通过采取一定的技巧，有效缓解BT基板翘曲的问题<sup>[7]</sup>。BT基板上具有覆铜区域，通过控制BT基板对称层的残铜比小于15%，可以有效避免基板翘曲问题。另外，通过在BT基板上的覆铜区域设置排气孔，基板上设置绿油层，也可以有效避免基板翘曲问题。

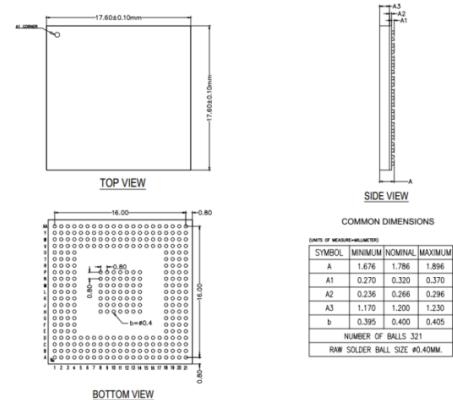

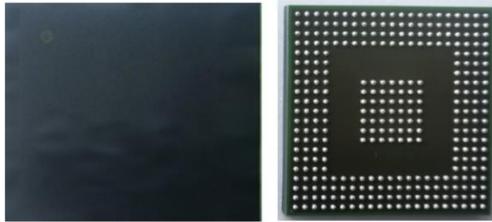

焊球采用材料 SAC305，直径 0.4 mm，通过 Wire-bond 工艺，研制出电机控制 SiP 电路的实物如图 4 所示。SiP 封装采用塑封 PBGA321，尺寸为 17.6 mm\*17.6 mm\*1.786 mm，pitch 为 0.8 mm，重

量为  $1.1 \text{ g} \pm 0.1 \text{ g}$ 。而 CKS32F407IGT6 芯片尺寸为  $26.1 \text{ mm} \times 26.1 \text{ mm} \times 1.6 \text{ mm}$ , 重量为  $2 \text{ g} \pm 0.1 \text{ g}$ ; 高云 GW1N-4K 型 FPGA 芯片尺寸为  $17 \text{ mm} \times 17 \text{ mm}$ 。由此可得电机控制 SiP 体积比 ARM 和 FPGA 分立器件设计的电机控制系统缩小了 50%以上, 重量减轻 60%以上。

图 4 SiP 电路的实物图

### 3 电机控制 SiP 电路测试系统设计

#### 3.1 测试系统设计

电机控制 SiP 电路内部集成了 ARM+FPGA, FPGA 主要负责信号的采集处理, ARM 实现系统控制。所设计的测试板也是以 ARM 和 FPGA 为核心, 通过实现对电机的精确控制测试其功能。

电机控制 SiP 电路测试系统框图如图 5 所示。SiP 电路置于测试插座中, 利用测试插座能够提高测试板的重复利用率<sup>[8-13]</sup>, 在设计的 SiP 的筛选电路中使用测试插座筛选出合格的 SiP 电路。该测试系统使用筛选后的 SiP 电路, SiP 最小系统及外设组成控制板, 信号隔离电路, IPM 功率模块, 电流采样等电路组成驱动板。

电机控制 SiP 测试中, 采用基于矢量控制策略的电机位置-速度-电流闭环控制方法。控制算法层实现 FOC 控制算法, 执行电机的位置控制、速度控制和电流闭环控制。由 ARM 处理器执行并调度相关计算任务。FPGA 模块通过硬件加速方式处理编码器位置采样, 并反馈给 ARM 处理器, 确保电机的精准控制。系统包含位置传感器、电流传感器等, 速度反馈通过位置信号差分获得, 用于实时监测电机的状态并反馈给 ARM 和 FPGA 模块。

图 5 电机控制 SiP 电路测试系统框图

#### 3.2 系统硬件设计

电机控制 SiP 电路测试系统主要包含四部分: 控制板、驱动板、被测电机、编码器转接板, 其中, 编码器转接板作用是将电机编码器输出 SCSI 接口转成螺钉端子, 方便接入到控制板编码器信号输入端, 驱动板排针接控制板控制信号输出, 驱动板电源分为控制电和功率电, 为两路 220V 交流输入, 分别为芯片供电和功率部分输出。测试系统实物图如图 6 所示。

图 6 测试系统实物图

#### 3.3 系统软件设计

##### 3.3.1 FSMC 通信原理介绍

FSMC (Flexible Static Memory Controller) 是 STM32 系列微控制器中用于连接外部存储器的硬件模块, 允许处理器与外部静态存储器进行高效的

数据交换。

系统利用FPGA进行正交编码器解码并获取位置反馈，而最终控制算法是在ARM端运行，因此需要将FPGA获得的实时位置反馈数据传输到ARM端，本系统采用的是FPGA将位置数据实时写入双端口RAM，ARM端读取RAM，这就需要ARM端的FSMC功能来读取RAM。

### 3.3.2 ARM端软件外设配置

通过STM32 CubeMX<sup>[14-15]</sup>可以方便的配置ARM端软件外设及时钟。其外设使用情况见表1。

表1 ARM端软件外设使用情况

| 外设     | 说明                                               |

|--------|--------------------------------------------------|

| ADC2   | 采集模拟量控制电压                                        |

| ADC3   | 采集U, V电流, 母线电压                                   |

| TIM8   | Channel1-3用于产生PWM控制信号<br>Channel4用于产生触发ADC采集中断信号 |

| FSMC   | 读取FPGA解码的编码器数据                                   |

| USART3 | RS485通信接口, Modbus通信                              |

(1) ADC外设配置：ARM端负责电流反馈采样，配置ADC为注入模式，选择TIM8外部触发源，来同步双通道的ADC采样，采样时间设置为28个时钟周期，来保障采样结果的准确性。(2) 定时器配置：TIM8为PWM输出定时器，中心对齐模式，死区时间系数配置为85，PWM输出模式选择MODE2，软件内根据控制算法计算出SVPWM的占空比，通过函数设置下发即可实现电机控制。(3) FSMC配置：配置外部外设类型为PSRAM，数据宽度选择8位，配置地址建立时间为10个时钟周期，地址保持时间为10个时钟周期，数据建立时间为15个时钟周期。

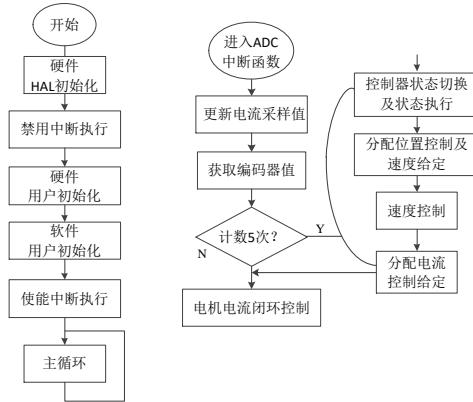

### 3.3.3 ARM端软件流程

通过高级定时器TIM8产生频率为10KHz的 PWM方波驱动电机转动，并触发ADC中断。调整TIM8的ADC触发比较值可以调整电流ADC采样的触发时刻，进而分配电流环控制的时间，实现电流采样与PWM的同步。ADC的触发和转换是硬件完

成的，不占用CPU时间，而转换完成时会产生中断，此时CPU响应中断进行电流环控制。通过合理利用ARM硬件资源，严格设计控制时序，采用硬件触发代替软件轮询，能够提高软件效率，保证控制的实时性。ARM端软件整体流程如图7所示。

图7 ARM端软件流程

电流、位置、速度信号处理在速度/位置模式下相同，电流采样通过计时器触发，触发频率为10KHz，在电流采样完成中断中进行电流反馈值计算，获得编码器读数，并进行电流环控制。速度环/位置环频率为2 kHz，其周期为电流环的5倍，则可在电流采样中断中计数5次执行速度(位置环)，速度(位置)环执行需要根据电机状态机分配模式及给定来源。

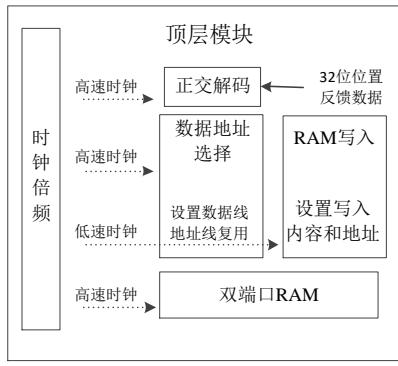

### 3.3.4 FPGA软件流程

FPGA主要实现了电机编码器位置数据解码和数据存储通信两部分功能，FPGA端软件架构图如图8所示。

(1) 数据解码。FPGA接收电机编码器输出的正交脉冲信号(A和B)，根据A和B信号的相位变化判断电机旋转方向，并通过计数器对脉冲信号计数来判断电机旋转位置增量，从而实现数据解码。

(2) 数据存储与通信。GOWIN的FPGA编程软件提供了SRAM实现的IP核，只需调用该IP核即可在FPGA中例化出一个双口RAM，一个端口可以用于存储电机编码器位置数据，另一个端口可以通过FSMC总线和ARM实现数据通信。

图 8 FPGA 软件架构图

## 4 测试结果

在电机控制系统中，尤其是位置控制和转速控制中，以下这些指标对系统性能和控制效果有着至关重要的影响。系统整体性能指标测试结果如表2所示。

逐一分析每个指标对电机控制的精度、稳定性、响应性等方面的影响。

表2 性能指标测试结果

| 序号 | 指标        | 测试结果                       |

|----|-----------|----------------------------|

| 1  | 最高正交解码频率  | 250 kHz以上                  |

| 2  | 并口通信速率    | 100 KB/s                   |

| 3  | 电流环控制频率   | 10 kHz                     |

| 4  | 位置速度环控制频率 | 2 kHz                      |

| 5  | 电流环控制抖动   | $\pm 5 \mu s$              |

| 6  | 位置速度环控制抖动 | $\pm 50 \mu s$             |

| 7  | 位置控制精度    | $\pm 10CNT$ @ 2500线编码器     |

| 8  | 转速控制精度    | $\pm 2RPM$ @ 额定转速、2500线编码器 |

| 9  | 转速稳定性     | 不大于1%                      |

| 10 | 转速超调量     | 不大于100 rpm                 |

| 11 | 位置超调量     | 不大于150 CNT                 |

(1) 最高正交编码器解码频率250 kHz，目的是保证速度较高时FPGA可以正确进行脉冲计数，对于2500线正交编码器而言，四倍频计数则电机旋转1圈计10000CNT，则250 kHz代表电机旋转速度为25 rps，测试中设置电机目标转速为50 rps，通过Free master观察位置反馈是否有突变可知，在速度上升至50 rps后，位置匀速增加，数据光滑无坏点，电机平稳运行，表明其正交解码频率满足250 kHz以上。

采用FPGA硬件加速编码器正交解码位置反馈，

确保系统能够在高速旋转下稳定跟踪电机位置，避免位置反馈丢失或误差的累积，提升了位置控制精度和转速响应速度。

(2) 并口通信速率测试在电流环中，读取三次FPGA传输的编码器数据，因为编码器数据32位，则读取1次编码器数据并口通信4 B数据，读取3次则并口通信数据12 B，ADC中断触发频率为10 kHz，则并口通信频率为120 KB/s，为更明显的显示数据是否有坏点，将读取的编码器数据依次加100，用Free master读取的数据波形，转动电机，可知其位置反馈无数据突变现象，表明并口传输速率120 KB/s可以保证。

通过FSMC接口和双端口RAM的实现，ARM端可以快速无误码地获取FPGA位置反馈结果，确保系统在高通信速率下能够稳定工作，尤其是在高动态负载变化时，系统能够快速传输和处理位置反馈信息，减少延迟，提升转速稳定性和电流环控制的响应速度。

(3) 电流环控制频率10 kHz，在电流环中反转IO口电平，并利用示波器测量。电流环控制频率设置为较高的采样率，以确保系统能够精确调节电机的电流和力矩输出。增强了系统的动态响应性。

(4) 位置速度环控制频率2 kHz，在位置速度环中反转IO口电平，并利用示波器测量。这种控制频率能在实际应用中平衡精度与系统负荷。确保了位置控制精度和转速控制精度。

(5) 电流环控制抖动，用示波器测量十次电流环执行时间，抖动范围满足 $\pm 5 \mu s$ 。通过对程序结构的合理设计，在实际应用中有效消除了电流环控制中的抖动现象。

(6) 用示波器测量十次位置环执行时间，抖动范围满足 $\pm 50 \mu s$ 。针对位置和速度环控制的抖动问题进行了充分优化。充分考虑芯片算力与算法计算耗时的配合，合理设计程序内中断执行方式及软件时序，防止出现控制过程被打断的情况。

(7) 通过2500线编码器反馈和FOC控制算法，实现了 $\pm 10$  CNT位置控制精度。使用下载器进入调试界面，直接观察位置控制下实际位置与给定位置变量，可得位置误差，满足指标要求。即使在高负载或复杂工况下，电机的位置误差始终保持在可接受的范围内。系统能够精确地定位至指定位置，无论是在启动、停止还是运行中，均能保持较小的定位误差。

(8) 转速随时间变化测试数据中最大偏离值为3000.2，转速控制精度在 $\pm 2$  rpm内。通过高效的控制算法，实现了转速的精确控制，并且系统能够在负载变化或速度突变时快速调整，保持稳定的目标转速。满足了大部分工业应用要求。

(9) 转速稳定性，速度变化率不大于1%。转速表测量某时刻输入直流电压170 V时转速，电机额定转速3000 rpm，输入额定电压220 V交流，转速为3000.3，满足指标。转速控制系统具备卓越的转速稳定性，通过高频率的反馈调节和适应性调整，即使在供电电压不满足额定电压时，电机转速仍能满足性能指标。

(10) 速度超调量不大于100 rpm。用Freemaster调试监控变量：查看速度整体变化过程图和速度逼近给定值50 rps时的效果图，换算为rpm即3 000 rpm，速度无超调。在转速调节过程中，通过优化PID控制参数，成功将转速超调量控制在较小范围内。这样即使在转速从零到满速的过渡过程中，系统也能平稳运行。

(11) 位置超调量不大于150 CNT。Free master软件调试监控变量位置整体变化曲线可知位置无超

**作者简介：**武明月（1989—），女，河南安阳人，硕士，工程师，主要研究方向为微系统、集成电路应用。

杜存玉（1995—），男，江苏徐州人，硕士，工程师，主要研究方向为嵌入式软件。

陈涛（1994—），男，湖北武汉人，硕士，工程师，主要研究方向为加固计算、机器视觉、集成电路测试应用。

艾亚辉（1990—），男，湖北安陆人，硕士，工程师，主要研究方向为智能制造装备。

调。在位置控制过程中，通过调整位置控制参数和引入适当的滤波器，成功抑制了位置控制中的超调现象。即使在快速变动的目标位置下，系统也能迅速稳定到目标位置。

## 5 结 论

本文设计了一款基于Wire-Bond工艺的电机控制SiP电路，相较于常规分立器件所搭建的机电控制系統其体积及重量均大幅度降低。针对该电机控制SiP电路，设计了SiP测试系統，通过对无刷电机控制的精确算法开发、硬件设计与实现，最终完成了基于矢量控制(FOC)的位置-速度-电流闭环控制系统，为SiP的可靠性分析提供了检测依据。

## 参考文献

- [1] 王梦雅,丁涛杰,顾林,等.面向信息处理应用的异构集成微系统综述[J].电子与封装,2021,21(10):11-30.

- [2] 陈晨,尹春燕,夏陈辉,等.垂直互联结构的封装天线技术研究[J].电子与封装,2023,23(7):1-12.

- [3] 张政楷,戴飞虎,王成迁.先进封装 RDL\_first 工艺研究进展[J].电子与封装,2023,23(10):1-10.

- [4] 倪宋斌,马美铭.集成电路成品测试的常见问题分析[J].电子与封装,2023,23(12):1-4.

- [5] 李杨,苏和平,张丹,等.基于 FPGA+ARM 多路千兆以太网通信接口设计[J].现代电子技术,2022,45(15):25-29.

- [6] Cadence. Cadence SiP design [EB/OL]. [2023-08-31]. [https://www.cadence.com/content/dam/cadence/www/global/en\\_US/documents/tools/ic-package-design-analysis/SiP-digital-design-ds.pdf](https://www.cadence.com/content/dam/cadence/www/global/en_US/documents/tools/ic-package-design-analysis/SiP-digital-design-ds.pdf).

- [7] 车岩.基于 ARM+FPGA 双核异构的 SiP 设计[J].微处理器,2024,24(1):15-18.

- [8] 杭万里,卜凡.SiP 电路的测试系統设计[J].数字技术与应用,2021,39(11):173-175.

- [9] 梅亮,赵鹏,高会壮.SiP 器件运行状态监测方法[J].舰船电子工程,2020,40(10):142-144.

- [10] 朱晓泉,周瑜,刘云飞,等.微系統技术发展现状及趋势[J].电声技术,2021,45(7):21-29.

- [11] 张昆.数字集成电路的测试技术应用[J].电子技术,2021,45(8):212-213.

- [12] 杨楚玮,张梅娟,侯庆庆.基于 FPGA 的 SiP 原型验证平台设计[J].电子技术应用,2022,48(1):84-88.

- [13] 许文运,张明,郑利华.基于先进工艺技术的机电控制 SiP 电路的设计与测试[J].电子技术应用,2024,50(11):105-108.

- [14] 陈启健,梁桃华,刘洪涛. STM32CubeMX 图形化配置方式与 MDK-ARM 代码开发方式比较[J].信息技术与信息化,2023(12):59-62.

- [15] 史记征.嵌入式系統开发课程理虚实一体化教学案例设计[J].电脑与电信,2025(1):93-100.